Block Diagrams

Features

| CPU | |

|---|---|

| Architecture | Arm® Cortex®-A53 |

| Processor | NXP® S32G399A CPU: 8 Arm® Cortex®-A53 64-bit cores, 4 Arm® Cortex®-M7 dual-core lockstep pairs |

| DRAM | 4 GB 32-bit soldered LPDDR4 RAM at 3200 MT/s |

| Memory | |

| Flash | 64 MB QSPI Flash |

| Flash Card | Interface for external SD-card multiplexed with eMMC |

| Boot Flash | Boot select: XSPI, eMMC or external SD card |

| eMMC | Up to 32 GB |

| Ethernet | |

| RGMII | 3x |

| SGMII | 3x 2.5 Gbps |

| High Speed IO | |

| SerDes lanes | 4x |

| ULPI-USB | 1x |

| PCIe | Yes |

| IO | |

| FlexSPI | 4x |

| UART | 2x |

| CAN FD | 18x |

| FlexRay | 2x |

| LIN | 4x |

| I2C | 4x |

| Analog Inputs (ADCs) | 12x |

| GPIOs | Yes |

| JTAG Debug Interface | Yes |

| Aurora Interface | Yes |

| Security / Safety | |

| Security | Hardware Security Engine (HSE) for secure boot and accelerated security services |

| Safety |

|

| Operating Condition | |

| Power Supply Voltage | Single DC power input (+9 V to +36 V) |

| Optional Power Supply Voltage | Single DC power input (+6 V to +36 V) |

| Power Management | Yes |

| RTC | RV-3028-C7 |

| Temperature | 0 °C to 70 °C |

| Optional Extended Temperature | -40 °C to +85 °C |

| Mechanical | |

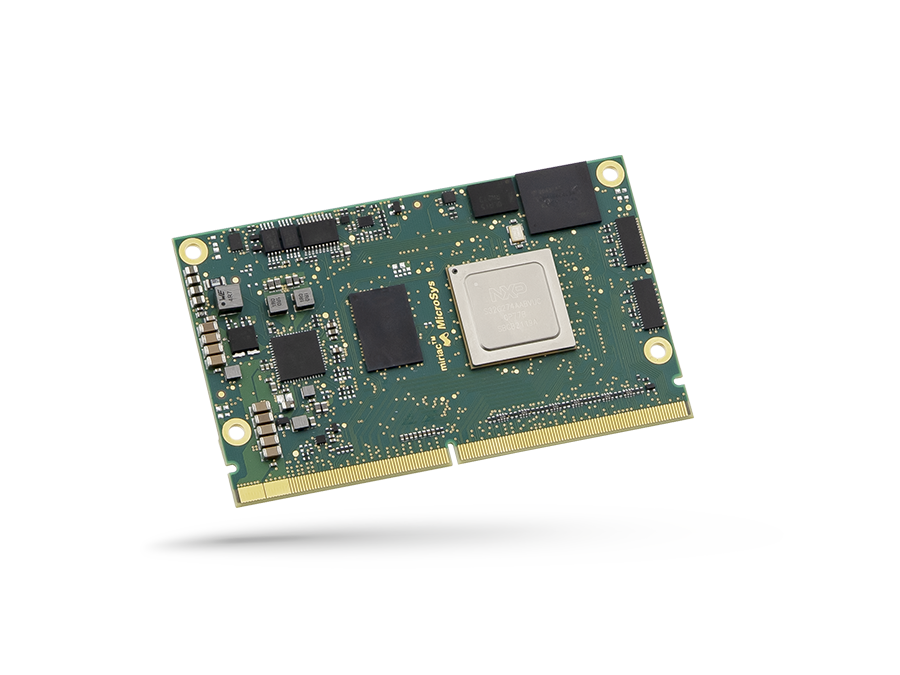

| Dimensions | 82 mm x 50 mm |

| Connector Type | MXM3.0 |

| Software / Additional | |

| Software Support |

|

| Additional |

|

Our standard product versions offer what we consider to be the optimum configuration in terms of performance, price, usage and TDP. The product features lists specify the maximum range of functions per interface. However, not all interfaces or functions are always available in parallel. Flexible SERDES multiplexing is one of the reasons for this. In addition, we provide multiple memory expansion options and are also happy to accommodate specific customer wishes. So do not hesitate to contact us directly to discuss your desired configuration.

Order Info

| Name | Code | Description | Status |

|---|---|---|---|

| miriac® MPX-S32G399A | 861703 | 8 Arm® Cortex®-A53, 1.3 GHz, 4 GB LPDDR4 w ECC, 64 MB NOR Flash, 16 GB eMMC, 0 °C to 70 °C, w SEC | active |

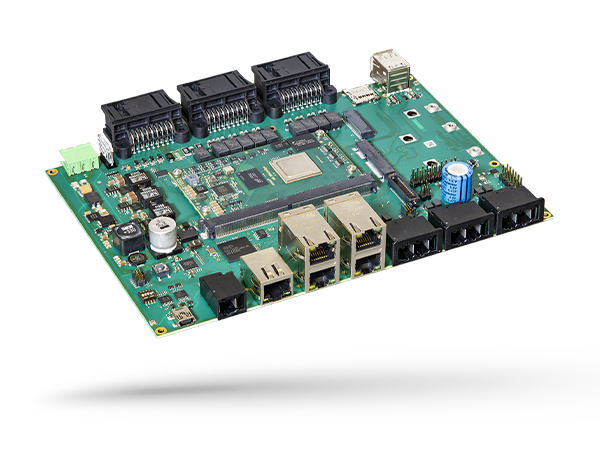

| Development Kit basic for miriac® MPX-S32G399A | 8629 |

|

active |

Downloads

FAQ

Q: Only eth0 (the top RJ45 on ST22) shows up as an interface on the S32G. How can I enable the other ethernet interfaces on the S32G?

A: If only eth0 shows up, have you checked that the PFE firmware is loaded ok in U-Boot? If yes, you will also have pfe0, pfe1, pfe2

Q: None of the SJA1110A ethernet ports link up. I’m guessing this is because I need to load an image on the SJA1110A.Is ST10 the JTAG header to use? What is J45 on the same header?

A: Yes, ST10 is the header to use. The other device in the JTAG chain, J45, is the Marvell 10GigE PHY (88X3310P) – which we have discarded on Rev.2 Carriers.

Q: Will the S32G detect the SJA1110A and forward traffic once an image is loaded or will I need another S32G image?

A: The SJA110 will forward traffic with the binary image loaded. But traffic coming from the S32G processor will need to be programmed to the SJA1110

Q: Is there a QSPI attached to the SJA1110, and is there a way for me to flash the QSPI?

A: Yes, there is a QSPI Flash attached to the SJA1110 which can be programmed using a Lauterbach debugger

Q: How do we select the boot mode for the SJA1110A?

A: When SW3 are both OFF, then you can program the Flash from debugger. When both switches are ON, the SJA1110 will boot from Flash

Q: In our environment, we need solutions that are available over a very long period of time (up to 15 years). How long are your modules available?

A: Using NXP CPUs on our SoMs we are able to provide an availability of 15 years from the time of the launch of the CPU. With LTB and long-time stocking we are even able to extend this period.